射频集成电路是现代无线通信系统的核心,其设计融合了模拟电路、数字电路、电磁场与微波技术,复杂度高,挑战众多。本文将系统解析射频集成电路设计中常见的几类关键问题及其应对方案。

一、 常见问题

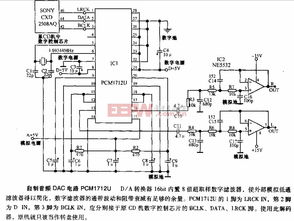

- 噪声与非线性失真:射频信号微弱,极易受到电路内部噪声(如热噪声、闪烁噪声)的干扰,导致信噪比下降。功率放大器、混频器等有源器件固有的非线性特性会产生谐波失真、交调失真,干扰有用信号甚至邻近信道。

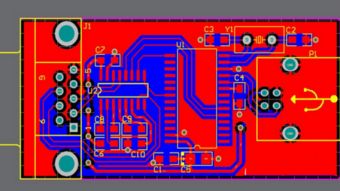

- 阻抗匹配与信号完整性:从芯片内部到封装、再到PCB板及天线,射频信号路径上的阻抗不连续会导致严重的信号反射和功率损耗。实现宽带、低损耗的阻抗匹配是设计难点。

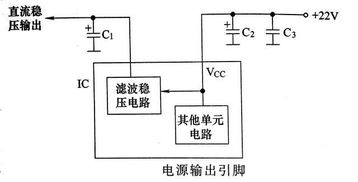

- 电源与衬底噪声耦合:数字电路部分开关动作产生的瞬态大电流会通过电源网络和公共硅衬底耦合到敏感的射频模拟部分,引起相位噪声恶化、接收机灵敏度下降等问题,即所谓的“噪声耦合”或“衬底噪声”。

- 工艺偏差与模型不确定性:CMOS等先进工艺的特征尺寸不断缩小,工艺波动(如阈值电压、栅氧厚度变化)对晶体管性能的影响愈发显著。高频下的器件模型(如MOSFET的BSIM模型)及无源器件(电感、变压器)模型可能存在精度不足的问题,导致仿真与流片结果存在差异。

- 功耗、线性度与效率的权衡:尤其在发射机功率放大器设计中,线性度、输出功率、效率和功耗之间存在固有的矛盾。提高线性度(如采用功率回退)往往以牺牲效率为代价,反之亦然。

- 测试与封装难度大:射频信号测试需要昂贵的专用仪器(如矢量网络分析仪、频谱分析仪),且探针、夹具引入的寄生效应会显著影响测量结果。封装寄生(引脚电感、焊盘电容)也会改变芯片性能,设计时必须预先考虑(“设计-封装协同设计”)。

二、 核心解决方案解析

- 应对噪声与非线性:

- 架构选择:采用低噪声放大器、镜像抑制混频器等有利于抑制噪声和特定失真的电路架构。

- 负反馈技术:合理应用负反馈(如电流-电流反馈)可以拓宽带宽、改善线性度,但需注意其对增益和稳定性的影响。

- 线性化技术:针对功放,可采用前馈、预失真(数字或模拟)等技术主动补偿非线性,在保证线性度的前提下提升效率。

- 优化偏置与器件尺寸:精心设计工作点和晶体管尺寸,在噪声、线性度和功耗之间找到最佳平衡点。

- 确保阻抗匹配与信号完整性:

- 片上无源元件优化:使用精准的电磁场仿真工具(如EMX, HFSS)对螺旋电感、变压器、传输线进行建模和优化,减小寄生,提高Q值。

- 匹配网络设计:采用L型、π型、T型等匹配网络结构,并利用Smith圆图工具进行设计和调谐,实现宽频带匹配。

- 协同仿真:将芯片、封装、PCB模型纳入统一仿真环境,进行系统级信号完整性分析。

- 抑制电源与衬底噪声:

- 物理隔离:采用深N阱、保护环(Guard Ring)将敏感的射频模块与数字模块在版图上隔离开。

- 电源分离与滤波:为模拟和数字部分提供独立的电源引脚和走线;在电源引脚处放置高性能的片上去耦电容;使用片上低压差线性稳压器为射频模块提供纯净电源。

- 差分电路结构:尽可能采用全差分电路设计,其对共模噪声(如衬底噪声)具有天然的抑制能力。

- 应对工艺偏差与模型问题:

- 稳健性设计:采用对工艺变化不敏感的电路拓扑,如电流模电路。设计足够的性能冗余(Margin)。

- 工艺角仿真与蒙特卡洛分析:在设计的各个阶段,进行涵盖典型、快、慢等多种工艺角的仿真,并结合蒙特卡洛统计分析,评估电路良率。

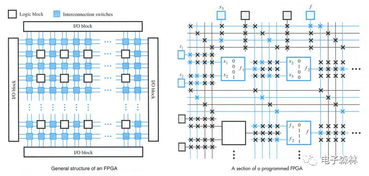

- 可调谐电路:引入可编程电容阵列、可调偏置电流等,在测试或工作时进行微调,以补偿工艺偏差。

- 优化功耗、线性度与效率:

- 先进功放架构:采用包络跟踪、异相发射、Doherty等高效架构,在不同输出功率水平下动态优化效率。

- 动态电源管理:根据通信标准的需求(如LTE的峰均比),动态调整偏置或电源电压,在低功率输出时降低功耗。

- 解决测试与封装难题:

- 设计-封装协同设计:在芯片设计初期就将封装模型(寄生RLC)纳入电路仿真,预留调整空间。

- 片上自测试:集成简单的检测电路(如功率检测器、频率计数器),辅助故障诊断和性能监控。

- 使用先进封装:考虑采用晶圆级封装、硅通孔等先进技术,显著减小封装寄生,提升系统性能。

射频集成电路设计是一项在多重约束下寻求最优解的工程艺术。成功的设计不仅依赖于设计师对器件物理和电路原理的深刻理解,更离不开缜密的系统规划、精准的建模仿真、对工艺的充分认知以及从芯片到系统的全局优化思维。随着5G/6G、物联网等技术的演进,这些挑战将更加严峻,相应的解决方案也将不断创新与发展。