随着无线通信技术向高速、低功耗、高集成度方向迅猛发展,专用射频集成电路(RFIC)已成为现代通信系统的核心。TH7122和TH71221作为两款高性能的射频收发芯片,为构建高速、可靠的无线数据链路提供了优秀的硬件基础。本文旨在探讨基于这两款集成电路的高速数据通信系统设计,并分析其关键设计考量与实现路径。

一、TH7122与TH71221芯片概述与特性

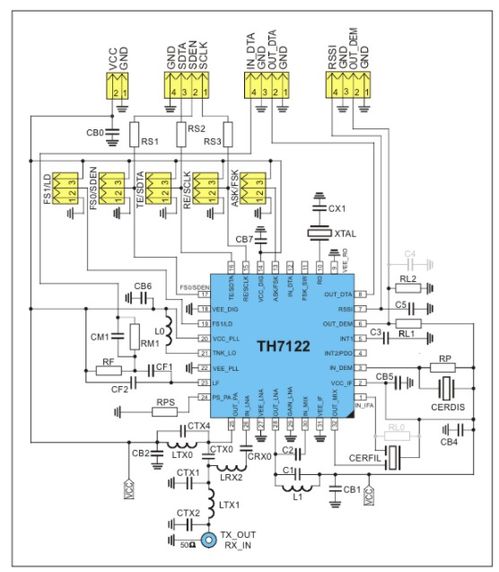

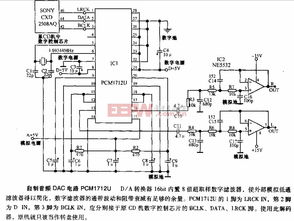

TH7122和TH71221是设计用于2.4GHz ISM频段的单片集成收发器。它们通常集成了完整的射频前端,包括低噪声放大器(LNA)、功率放大器(PA)、混频器、压控振荡器(VCO)以及频率合成器等关键模块。其中,TH7122系列可能更侧重于基础收发功能,而TH71221则在集成度、数据率支持或特定性能指标上有所增强(注:具体参数需以官方数据手册为准)。其共同特点包括支持FSK/GFSK/MSK等高效调制方式,具备较高的接收灵敏度与输出功率,以及通过SPI接口实现灵活的数字配置,这为高速数据通信(通常指达到Mbps量级的数据传输率)奠定了物理层基础。

二、高速数据通信系统架构设计

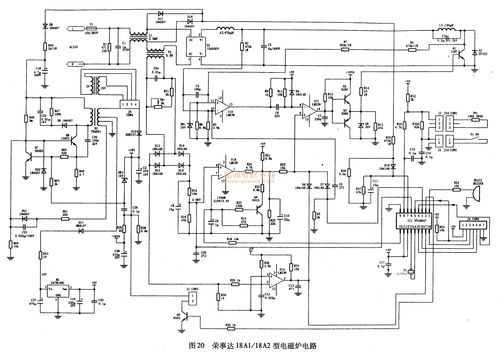

一个完整的高速无线通信系统,除射频前端外,还需包含基带处理、协议控制与接口单元。基于TH7122/TH71221的系统典型架构如下:

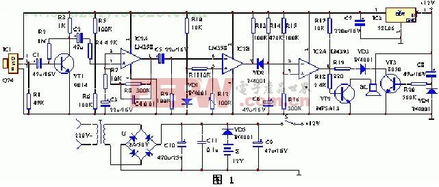

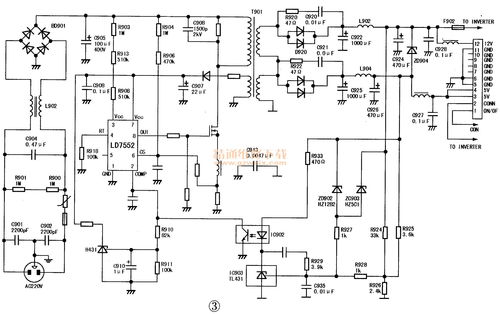

- 射频前端模块:以TH7122或TH71221为核心,负责信号的调制、发射、接收与解调。设计重点在于外围匹配电路(如天线匹配、滤波器)、晶体振荡器选择以及电源去耦,以确保射频性能稳定,满足目标频段、带宽和发射谱模板要求。

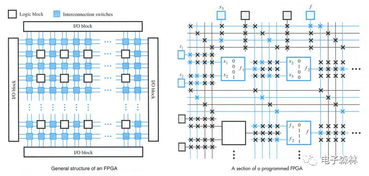

- 基带处理器/微控制器单元:选用一款具备足够处理能力(如ARM Cortex-M系列)和高速SPI/DMA接口的MCU或专用基带芯片。该单元负责实现通信协议(如自定义协议或简化版IEEE 802.15.4)、数据组帧/解帧、前向纠错(FEC)、循环冗余校验(CRC)以及控制射频芯片的寄存器配置。对于高速数据传输,处理器的速度与射频芯片的数据吞吐能力必须匹配。

- 协议与数据流设计:为实现高速率,需优化物理层与数据链路层。这包括选择适当的调制指数与数据率配置(在芯片允许范围内),设计高效的数据包结构以减少开销,并可能采用自适应速率等策略来平衡速率与链路可靠性。

三、集成电路设计关键考量与挑战

在采用此类商用射频IC进行系统设计时,需从集成电路应用的角度关注以下要点:

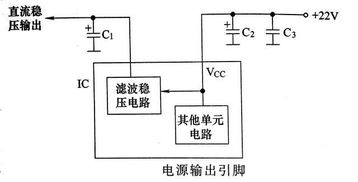

- 电源完整性与噪声管理:高速数字电路(MCU)与模拟射频电路共存于同一PCB上,电源噪声和数字开关噪声会严重影响射频性能。设计中必须采用星型电源拓扑、多层板分隔地平面、大量使用去耦电容和磁珠进行隔离。TH7122/TH71221的模拟电源(如VCO、LNA电源)尤其需要洁净的供电。

- 参考时钟设计与相位噪声:芯片的参考时钟(通常来自外部晶体)的相位噪声直接影响到系统的误码率(BER)和邻道抑制能力。需选择低相位噪声的晶体并设计优化的振荡电路,布局上应紧靠芯片相关引脚,并远离噪声源。

- PCB布局布线:这是射频设计成败的关键。需严格按照数据手册的推荐进行布局,确保射频走线(特别是RX输入、TX输出、VCO电感等路径)短而直,阻抗控制精确(通常为50欧姆)。数字控制信号(如SPI、GPIO)应避免穿越或靠近敏感射频区域,必要时可增加地屏蔽过孔。

- 天线接口与匹配:天线是整个通信链路的最终环节。必须根据芯片输出阻抗和天线阻抗,设计精确的π型或L型匹配网络,并使用矢量网络分析仪(VNA)进行调试,以实现最大功率传输和最佳辐射效率。

四、性能优化与测试验证

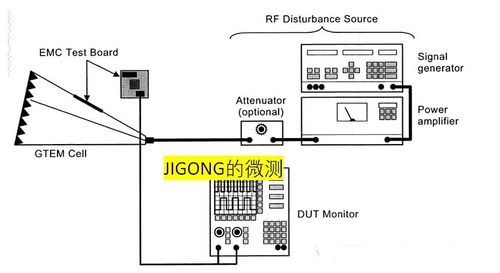

系统搭建完成后,需进行一系列测试以验证其高速通信能力:

- 传导测试:通过电缆连接,测试发射功率、频谱模板、接收灵敏度、误码率(BER)与数据率的关系。

- 无线吞吐量测试:在实际环境中,测试端到端的有效数据吞吐量,评估协议开销和实际环境(多径、干扰)对高速传输的影响。

- 功耗测试:测量不同工作模式(发射、接收、休眠)下的电流消耗,这对于电池供电的应用至关重要。

基于TH7122和TH71221集成电路设计高速数据通信系统,成功的关键在于深刻理解芯片特性、 meticulous的射频PCB设计以及稳健的基带协议实现。通过精心设计,这两款芯片能够支撑起高性能的短距离无线数据链路,广泛应用于工业控制、高速数据采集、高级人机交互设备等众多领域,体现了现代射频集成电路在推动通信技术发展中的核心价值。